In alternativa ai tradizionali MOSFET al silicio, i MOSFET al carburo di silicio (Sic) offrono i vantaggi di una maggiore tensione di blocco, minore resistenza allo stato on e maggiore conduttività termica. I dispositivi possono sostituire MOSFET al silicio e IGBT in molte applicazioni.

Perché scegliere i dispositivi SiC?

I MOSFET in carburo di silicio (SiC) mostrano una tensione di blocco più elevata, una resistenza di stato inferiore e una conduttività termica più elevata rispetto alle loro controparti in silicio. I MOSFET SiC sono progettati ed essenzialmente elaborati allo stesso modo dei MOSFET in silicio. Le prestazioni migliorate derivano dai vantaggi materiali inerenti alla fisica del carburo di silicio. Grazie alla sua struttura semplice, alla facilità di progettazione e alle basse perdite di pilotaggio, il MOSFET SiC con modalità di miglioramento del canale N offre una buona compatibilità in sostituzione dei MOSFET al silicio e degli IGBT.

Quale nomenclatura utilizzano i dispositivi SiC?

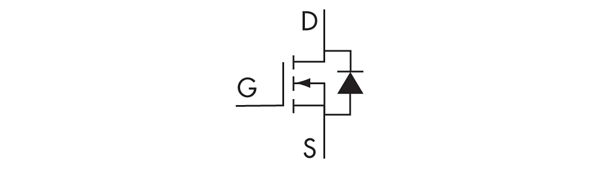

I transistor SiC hanno preso in prestito la stessa nomenclatura dei loro fratelli in silicio: gate, drain e source, come mostrato in Fig.1. Inoltre, la resistenza on e la tensione di rottura di un dispositivo SiC hanno un significato simile a quello delle loro controparti in silicio. Le curve di tensione On-Resistance (RDS (ON)) e gate-source sono simili a quelle dei MOSFET al silicio. Il coefficiente di temperatura della resistenza ON del MOSFET SiC è simile a quello del MOSFET al silicio in quanto è positivo, ma l’entità della variazione di RDSon è inferiore nell’intervallo operativo del dispositivo.

Storia dei transistor SiC

Come si è evoluto il transistor SiC ? L’adozione di semiconduttori SiC è stata limitata dai costi del substrato, dalle peculiarità fisiche del materiale e dalla densità dei difetti. Questi problemi hanno limitato la diffusione dei dispositivi SiC ai diodi negli ultimi cinque anni. Tuttavia, i problemi di elaborazione dei wafer sono stati in gran parte risolti con lo sviluppo di wafer SiC a basso difetto che consentono di produrre MOSFET SiC. Cree ha introdotto il primo MOSFET SiC nel gennaio 2011. Questo transistor CMF20120D era valutato a 1200 V, aveva una resistenza di 80 mΩ ed era alloggiato nel contenitore TO-247. Sebbene il suo costo fosse superiore a quello dell’IGBT Si che avrebbe dovuto sostituire, i MOSFET SiC hanno una commutazione più rapida, una migliore efficienza e migliori prestazioni termiche. Il MOSFET SiC di seconda generazione, C2M0080120D, è stato rilasciato a marzo 2013 e presenta caratteristiche prestazionali migliorate. La tabella 1 confronta i parametri chiave del dispositivo delle parti di prima e seconda generazione. Si noti, in particolare, la riduzione delle dimensioni dello stampo e dei valori di capacità associati. Ciò contribuisce alla migliore efficienza di commutazione del dispositivo Gen2 e anche alla notevole riduzione dei costi.

Moduli di Potenza

Esistono moduli di potenza MOSFET SiC?

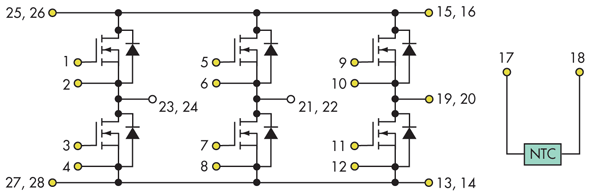

Cree ha introdotto il primo modulo di alimentazione a sei componenti in carburo di silicio (SiC) disponibile in commercio in un package standard da 45 mm (Fig. 2). Quando si sostituisce un modulo in silicio con valori nominali equivalenti, il modulo six-pack di Cree riduce le perdite di potenza del 75 percento, il che porta ad una riduzione immediata del 70 percento delle dimensioni del dissipatore di calore o ad un aumento del 50 percento della densità di potenza. Il modulo SiC a sei componenti sblocca i tradizionali vincoli di progettazione associati a densità di potenza, efficienza e costi, consentendo così al progettista di creare sistemi di conversione di potenza ad alte prestazioni, affidabili e a basso costo.

Quali gate driver possono essere utilizzati con un MOSFET SiC?

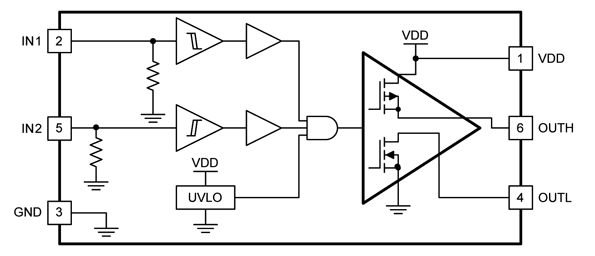

I circuiti integrati gate driver adatti per MOSFET SiC sono disponibili da IXYS, Texas Instruments e più recentemente da Avago. La famiglia di circuiti integrati UCC2753x di Texas Instruments è costituita da gate driver a canale singolo, ad alta velocità, in grado di pilotare interruttori di potenza MOSFET SiC con una sorgente fino a 2,5 A e una corrente di picco sink (azionamento asimmetrico) di 5 A (Fig.3). La forte capacità di caduta nell’azionamento asimmetrico aumenta l’immunità contro l’effetto parassitario di attivazione di Miller. L’UCC2753x può anche essere dotato di una configurazione a uscita divisa che consente al progettista di applicare resistori di accensione e spegnimento indipendenti rispettivamente ai pin OUTH e OUTL e di controllare facilmente le velocità di variazione della commutazione.

Il driver ha capacità di pilotaggop rail-to-rail e un ritardo di propagazione estremamente ridotto, tipicamente 17 ns. La soglia di ingresso di UCC2753xDBV si basa sulla logica a bassa tensione compatibile TTL e CMOS, che è fissa e indipendente dalla tensione di alimentazione VDD. La sua isteresi tipica di 1V offre un’eccellente immunità ai disturbi.

IXD_609SI di IXYS è un gate driver ad alta velocità di grado automobilistico. La sua uscita può generare e assorbire 9 A di corrente di picco, producendo tempi di salita e discesa inferiori a 45 ns. Sia l’uscita che l’ingresso hanno una tensione nominale di 35 V. L’ingresso è virtualmente immune al latch-up e i circuiti proprietari eliminano la conduzione incrociata e lo “shoot-through”. L’IXD_609SI ha un intervallo di temperatura operativa ambiente di Grado 1, da -40 ° C a +125 ° C. È certificato AEC Q100 edcè disponibile in un package Power SOIC a 8 pin con retro in metallo esposto.

L’ACPL-P346 di Avago è un fotoaccoppiatore gate drive da 2,5 A ad alta velocità che contiene un LED AlGaAs, accoppiato otticamente ad un circuito integrato con uno stadio di uscita di potenza. Questo fotoaccoppiatore è ideale per il pilotaggio di MOSFET SiC e di potenza utilizzati in applicazioni di inverter o convertitori AC-DC / DC-DC. L’elevato intervallo di tensione operativa dello stadio di uscita fornisce le tensioni di pilotaggio richieste dai dispositivi controllati da gate. La tensione e l’elevata corrente di uscita di picco fornita da questo fotoaccoppiatore lo rendono ideale per MOSFET a pilotaggio diretto ad alta frequenza per la conversione ad alta efficienza. L’ACPL-P346 ha la tensione di isolamento più alta di VIORM = 891 V di picco in IEC / EN / DIN EN 60747-5-5 ed è UL1577 riconosciuto con 3750 VRMS per 1 minuto.

Ottimizzazione del layout

Come si ottimizza il layout per garantire un corretto pilotaggio del gate?

Per ottenere tempi di commutazione rapidi, le interconnessioni del gate drive devono avere un minimo di parassiti, in particolare induttanza. Ciò richiede che il gate driver sia posizionato il più vicino possibile al C2M0080120DD. Prestate ttenzione nella selezione di un resistore di gate esterno appropriato per gestire il superamento della tensione e la suoneria. – Il ringing più alto può essere un problema, perché la transconduttanza inferiore e la tensione di soglia bassa del C2M0080120D di / dt possono accoppiarsi al circuito di gate attraverso qualsiasi induttanza gate / source comune. La ferrite aiuta a ridurre al minimo il ringing mantenendo un tempo di commutazione rapido. È necessario utilizzare un resistore di valore elevato (10 kΩ) tra gate e source per evitare un flottante eccessivo del gate durante i ritardi di propagazione all’accensione del sistema.

Il MOSFET SiC ha un diodo di body ?

Come i MOSFET al silicio convenzionali, il MOSFET SiC ha un diodo di body – un PN con tensione di soglia da 3,1 V a 3,3 V. La tensione di accensione più elevata riduce leggermente l’efficienza rispetto a un diodo Schottky SiC esterno, ma il diodo di body ha una carica di recupero inversa molto inferiore rispetto al diodo di body di un MOSFET al silicio.

Come si confronta l’efficienza delle due generazioni di MOSFET SiC con quella degli IGBT al silicio?

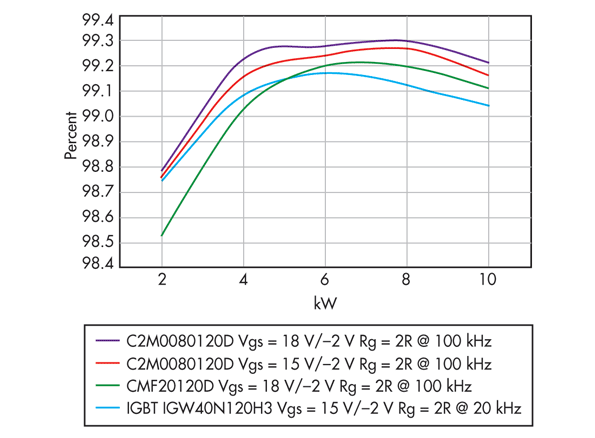

La Figura 4 mostra i dati dei test di efficienza con i MOSFET SiC a 100 KHz (MOSFET SiC di prima generazione CMF20120D e MOSFET SiC di seconda generazione C2M0080120D) e Si IGBT (IGW40N120H3) a 20 KHz. I diodi di uscita utilizzati per entrambi i dispositivi di commutazione è il diodo Schottky Cree 1200 V SiC C4D10120D, garantendo così un confronto equo. Tutti i dati si basano su un resistore di gate esterno di 2 Ω. Anche con una frequenza di commutazione cinque volte superiore , la soluzione SiC è stata in grado di raggiungere un’efficienza massima del 99,3% a 100 KHz, riducendo le perdite del 18% dalla migliore efficienza della soluzione IGBT a 20 KHz. A carichi leggeri, dove i due progetti mostrano la minore efficienza, la soluzione SiC a 100 KHz corrispondeva ancora alle prestazioni a 20 KHz del sistema al silicio. Questo confronto mostra che il MOSFET SiC possiede sia una migliore efficienza che un vantaggio in frequenza rispetto a un IGBT al silicio. È quindi possibile progettare sistemi altamente efficienti con MOSFET SiC a frequenze di commutazione che consentono valori inferiori degli elementi magnetici, riducendo le dimensioni, il peso e il costo complessivi del sistema.

Riduzione delle interferenze elettromagnetiche

Cosa si dovrebbe fare per ridurre al minimo le EMI nei circuiti MOSFET SiC?

Per La progettazione EMI bisognerebbe prestare attenzione con dispositivi di alimentazione SiC ad alta frequenza . Esistono alcuni approcci pratici che possono essere utilizzati per limitare l’influenza del rumore con un’elevata frequenza di commutazione. Con un’elevata frequenza di commutazione e tempi di commutazione rapidi dei MOSFET SiC, il ringing della tensione di drain è potenzialmente molto più elevato a causa dell’oscillazione parassita, soprattutto a causa della capacità parassita dell’induttore. Quando gli interruttori del circuito sono di accensione e spegnimento, c’è una risonanza ad alta frequenza tra la capacità parassita dell’induttore e l’induttanza parassita nel circuito di commutazione, che porterà a un ringing eccessivo. Per ridurre il ringing ad alta frequenza, utilizzate un induttore di avvolgimento a strato singolo. Un avvolgimento a strato singolo può ridurre drasticamente la capacità parassita dell’induttore con un buon accoppiamento di flusso. Ciò comporterà una riduzione degli squilli all’interno del nodo di commutazione VDS.

Leggi l’articolo originale e completo su Power Electronics