La scorsa puntata abbiamo studiato le operazioni di importazione dei componenti elettronici sia a livello di modello che a livello di sotto-circuito. In questo articolo eseguiremo alcune analisi di circuiti di potenza utilizzando i componenti della libreria interna di QSPICE. Dopo una breve panoramica dei componenti di potenza disponibili nella libreria interna saranno eseguite alcune analisi di circuiti di potenza di base, realizzando che la qualità del software utilizzato è davvero molto elevata in questo genere di simulazioni.

Introduzione

QSPICE, già alla sua prima uscita, ha inserito una libreria di componenti semiconduttori di potenza e allo stato attuale, almeno alla data della scrittura del presente articolo, il software mette a disposizione dell’utente, in una libreria interna e facilmente utilizzabile, le seguenti categorie di componenti di potenza:

-

- JFET 650 V

- JFET 1200 V

- JFET 1700 V

- SiC FET 650 V

- SiC FET 1200 V

- SiC FET 1700 V

- SiC Schotty

Avere in libreria una raccolta di elementi di potenza è un ottimo punto di partenza per la progettazione di un sistema funzionante. Questi elementi possono essere utilizzati per creare circuiti di base, come alimentatori, inverter e regolatori di tensione. Se poi è necessario utilizzare un modello specifico di componente, è possibile importarlo da un file esterno. Questo è utile se si desidera utilizzare un componente che non è disponibile nella libreria predefinita.

Analisi statica di un SiC FET

Per gli esempi del presente articolo sarà utilizzato il SiC FET UF3C120400K3S, già presente nella libreria di QSPICE. Il dispositivo è disponibile nel contenitore TO-247-3L e presenta una carica di gate ultra bassa ed eccezionali caratteristiche di recupero inverso, rendendolo ideale per la commutazione di carichi induttivi e qualsiasi applicazione che richiedono un azionamento standard. Dal suo datasheet ufficiale (e invitiamo gli utenti a leggere attentamente tale documento), ecco alcuni suoi parametri più utili e importanti, che il progettista deve conoscere, ai fini di una progettazione coerente ed esente da errori:

-

- typical RDS (on): 0.410 ohm;

- maximum operating temperature: 175 °C;

- maximum drain-source voltage (Vds): 1200 V;

- maximum gate-source voltage (Vgs): from -25 V to 25 V;

- maximum continuous drain current (TC=25 °C): 7.6 A;

- maximum oower dissipation: 100 W.

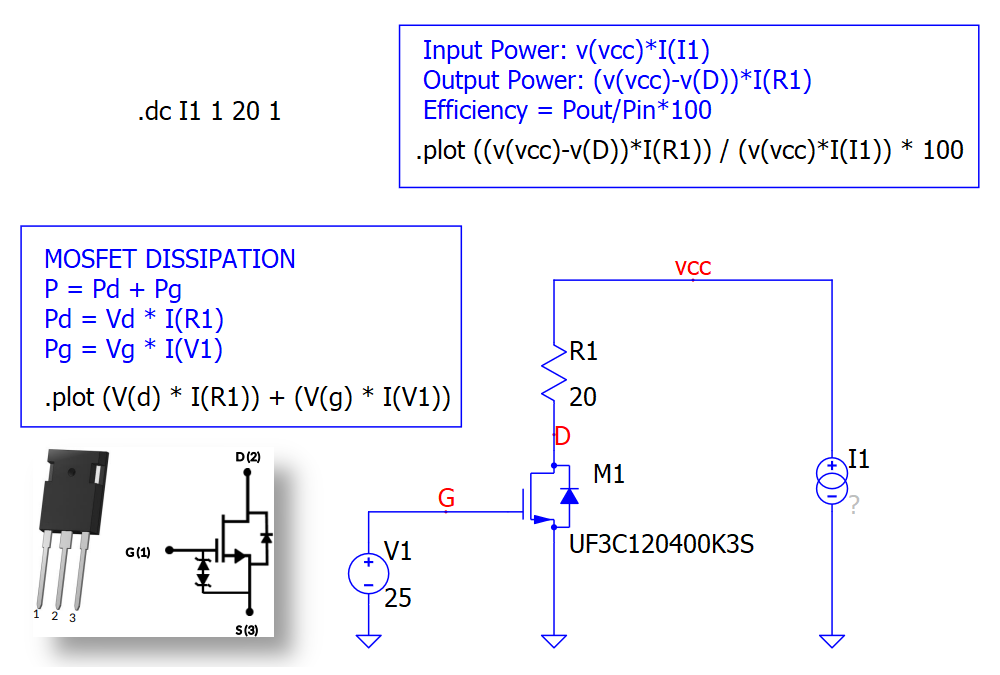

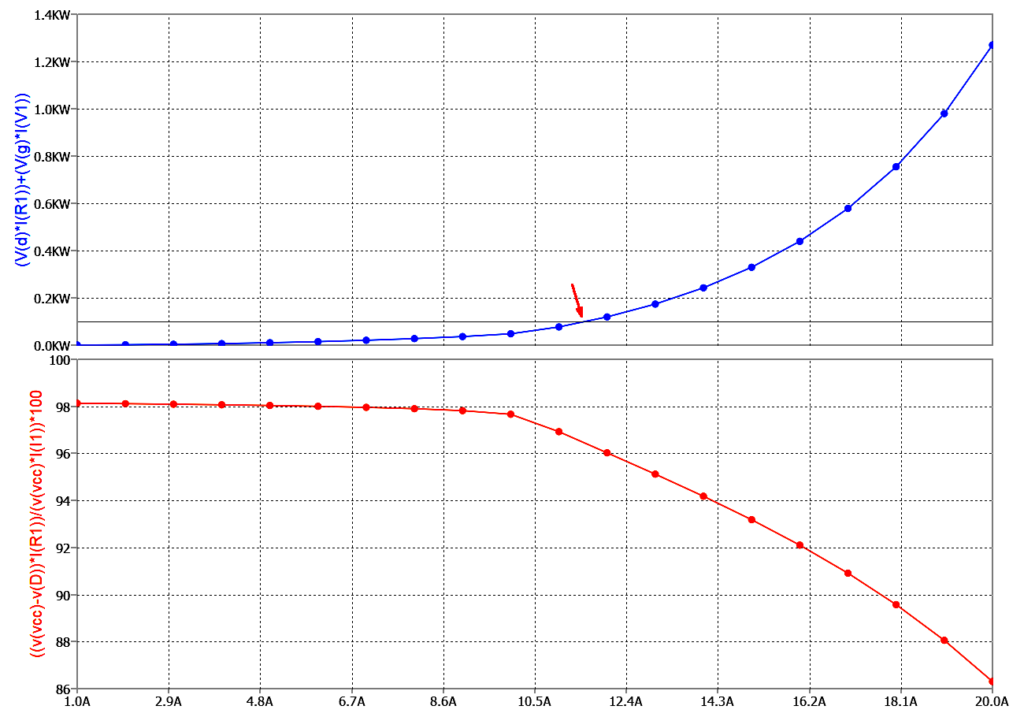

In figura 1 è mostrato un circuito di test che prevede l’alimentazione di un carico resistivo (R1) di 20 ohm. Lo schema è formato da un generatore di corrente (I1), da un generatore di tensione per il pilotaggio del gate (V1) e dal dispositivo M1 modello UF3C120400K3S. Il gate risulta sempre alimentato, pertanto il FET è sempre in stato di conduzione. La simulazione esamina il circuito con correnti di alimentazione comprese tra 1 A e 20 A, con continuità, grazie alla direttiva SPICE:

.dc I1 1 20 1

E tramite le direttive “.plot” vengono visualizzati gli oscillogrammi relativi.

Figura 1 – Lo schema elettrico del generatore PWM.

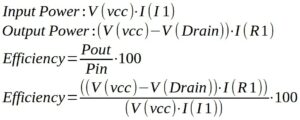

Il grafico mostrato in figura 2 mette in evidenza due importanti parametri del circuito:

-

- la potenza dissipata dal FET SiC, in relazione alla corrente di drain;

- l’efficienza del sistema, sempre in relazione alla corrente di drain.

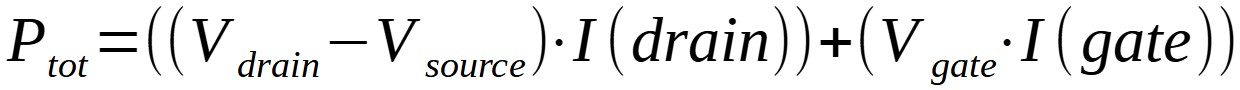

Relativamente al primo grafico, situato in alto, è mostrata la potenza dissipata dal FET SiC UF3C120400K3S, variando la corrente che scorre sul suo drain. La simulazione prevede volutamente una dissipazione di potenza molto più elevata di quella che lo stesso componente può sopportare. Per fortuna tale fatto può essere permesso nelle simulazioni. La potenza dissipata dal FET SiC è calcolata nel seguente modo:

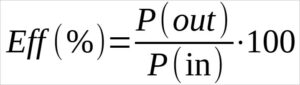

Nella pratica si considera solo il prodotto della tensione di drain per la corrente di drain, dal momento che la corrente di gate è irrilevante e nell’ordine dei nanoAmpere. Si ricorda che la massima potenza ammessa dal FET è di 100 W, valore che viene di proposito superato nella simulazione, al fine di analizzare i comportamenti del circuito in caso di condizioni di sovraccarico. Questo fatto può essere utile per identificare potenziali problemi di affidabilità o di sicurezza del circuito. Relativamente al secondo grafico, situato in basso, l’efficienza del circuito è determinata secondo la seguente formula generale:

e in particolare:

Come si vede dal grafico dell’efficienza (grafico rosso in basso), l’efficienza media per tutto il range di potenza riconosciuto dal produttore è del 98% circa, e in effetti si tratta di una ottima efficienza. Ma se la potenza dissipata dal FET inizia a superare i 100 W (limite imposto nel relativo datasheet), l’efficienza del sistema inizia a calare drasticamente a valori non più ottimali e pericolosi. In tali condizioni, il dispositivo potrebbe anche essere distrutto dal calore.

Figura 2 – I grafici della potenza dissipata dal FET (in alto) e dell’efficienza del sistema (in basso).

Il generatore PWM

Un generatore PWM produce un segnale digitale che consiste in una serie di impulsi di uguale ampiezza, ma di larghezza variabile. La larghezza dell’impulso, nota come duty cycle, determina l’intensità del segnale analogico equivalente. Esso può essere utilizzato per controllare la potenza erogata su una varietà di dispositivi, come motori elettrici, LED e lampade, alimentatori e altro. Il duty cycle di un segnale PWM può essere regolato facilmente modificando opportunamente le durate del segnale a livello alto (Ton) e quello a livello basso (Toff). Un duty cycle più alto corrisponde a un equivalente segnale analogico più intenso. Si precisa che non è la frequenza del segnale a determinare gli effetti sul carico ma la durata dell’impulso attivo. Pertanto, a parità di duty cycle, due segnali caratterizzati da frequenze differenti producono gli stessi effetti. L’esempio che segue (il cui schema elettrico è osservabile in figura 3) prevede la simulazione di un sistema di generazione PWM che alimenta un carico resistivo. Il generatore V1 emette un segnale PWM con duty cycle del 50% alla frequenza di circa 30 khz, con una ampiezza (in stato di ON) di 25 V, adatta al pilotaggio del gate del FET SiC. L’alimentazione del sistema è di 96 V mentre il carico è di 20 ohm.

Figura 3 – Lo schema elettrico di un sistema di generazione PWM che alimenta un carico resistivo.

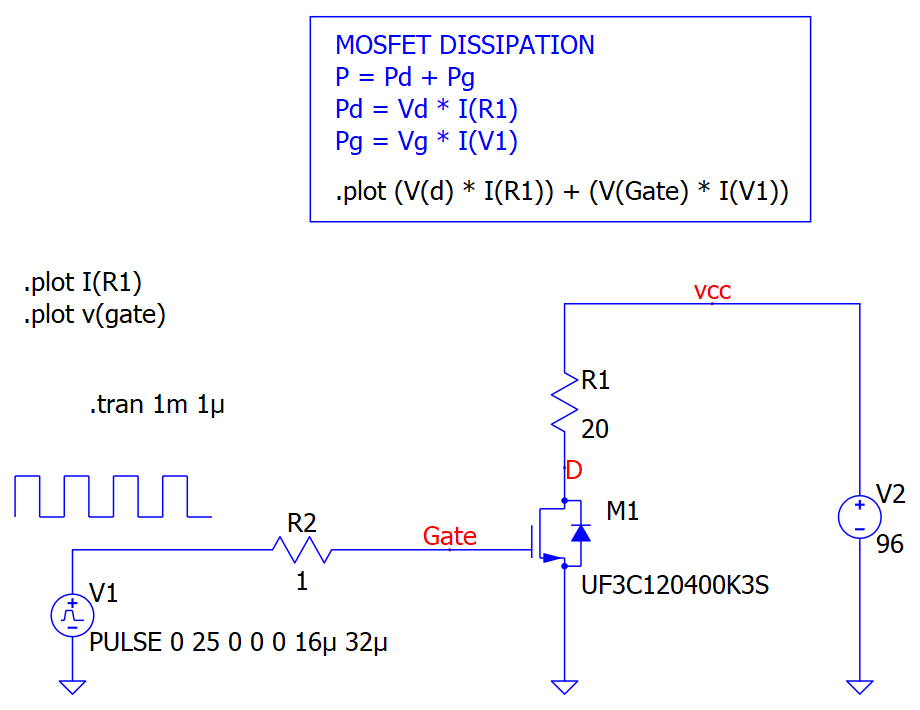

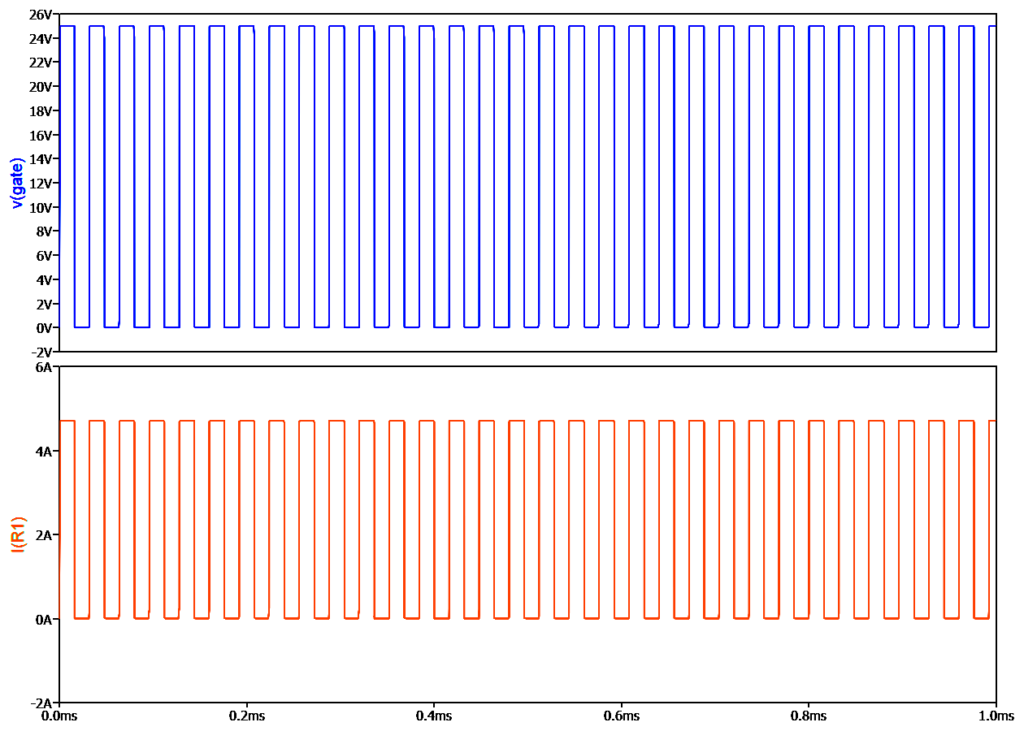

Il generatore PWM genera, dunque, un segnale impulsivo e lo stato ON, temporalmente equivalente allo stato OFF, ha una durata di 16 microsecondi. Osservando i grafici dei segnali, in figura 4, sembrerebbe a prima vista che il sistema sia perfetto ed esente da problemi e che il suo funzionamento sia ottimale. La tensione di gate (in alto) e la corrente sul carico (in basso) seguono, infatti, un andamento pulito e senza apparenti problematiche.

Figura 4 – Un grafico panoramico della corrente sul carico non evidenzia, apparentemente, la presenza di problemi nel circuito.

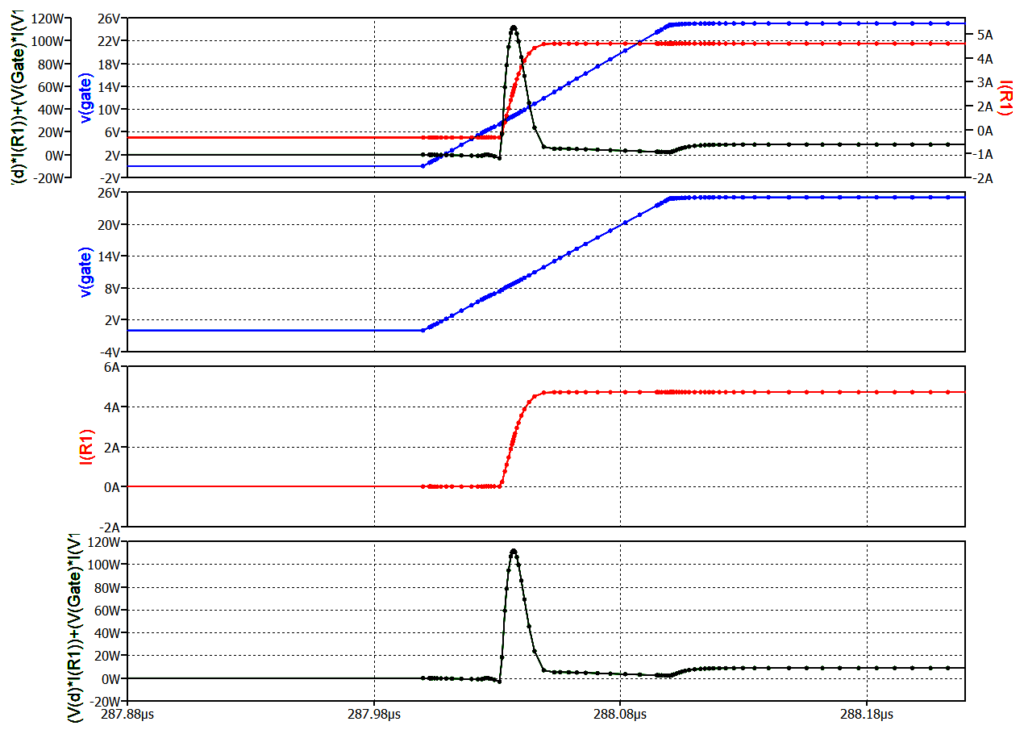

Occorre, invece, ricordare che i componenti elettronici, specialmente di commutazione, presentano caratteristiche non ideali come, ad esempio, le cadute di tensione non nulle e le transizioni di commutazione non istantanee. Queste caratteristiche possono limitare il funzionamento del componente, specialmente a velocità elevate o a regimi energetici importanti. E’ sufficiente, infatti, visualizzare anche il grafico della dissipazione di potenza del FET SiC e ingrandire il diagramma sul fronte di salita o di discesa del segnale, per iniziare a scorgere le prime problematiche. In figura 5 è raffigurato il grafico in corrispondenza del fronte di salita e le tracce mostrate sono le seguenti:

-

- la prima traccia in alto contiene tutti i segnali in oggetto, nello stesso grafico;

- la seconda traccia contiene la tensione di gate del FET SiC;

- la terza traccia contiene la corrente sul carico R1;

- la quarta traccia contiene la potenza dissipata dal FET SiC.

La transizione è molto breve, nell’ordine delle decine di nanosecondi, ma in questo frangente il FET ha un comportamento in regime lineare e la sua commutazione è graduale e non immediata. Esiste una zona transitoria, pertanto, in cui sia la corrente che la tensione sono contemporaneamente positive e generano una perdita di commutazione che può risultare fatale. Anche la legge di Ohm conferma tale fatto. Tali perdite sono, oggi, inevitabili e si verificano, come detto prima, durante i fronti di commutazione in salita e in discesa. Tuttavia esistono molte tecniche, hardware e software, per ridurle a livelli abbastanza accettabili. La perdita di commutazione, benché sia caratterizzata da una durata estremamente bassa, causa problematiche sul valore medio dei segnali di tensione, di corrente e di potenza e genera anche disturbi a livello RF.

Figura 5 – Durante le transizioni OFF-ON e ON-OFF dei dispositivi avvengono importanti perdite di commutazione.

Conclusioni

Con QSPICE la simulazione dei componenti elettronici di potenza è molto efficiente e, soprattutto, esente da problematiche operative spesso comuni con altri simulatori. Esso è un valido strumento che può aiutare i progettisti a progettare sistemi più affidabili e sicuri, senza utilizzare alcun componente reale. In questa maniera si possono ridurre i tempi e i costi di sviluppo riducendo, nel contempo, il rischio di fallimento del progetto. Le simulazioni possono essere utilizzate per studiare le condizioni di sovraccarico o per testare diverse velocità operative di commutazione, modificando solo pochi parametri.

Autore: Giovanni Di Maria